| Contents | Previous Chapter | Next Chapter |

The term Stability is of central importance for the treatment of finite state machines. The FSM stability depends on the intended mode of operation, i.e. a distinction has to be made in asynchronous and synchronous operation.

Similar to what has been seen in the treatment of Flip-Flops, an asynchronous FSM will be in a stable state when the following is valid for all feedbacks:

Obviously this criteria defines stability as the state in which no signal changes are occurring in the feedback path.

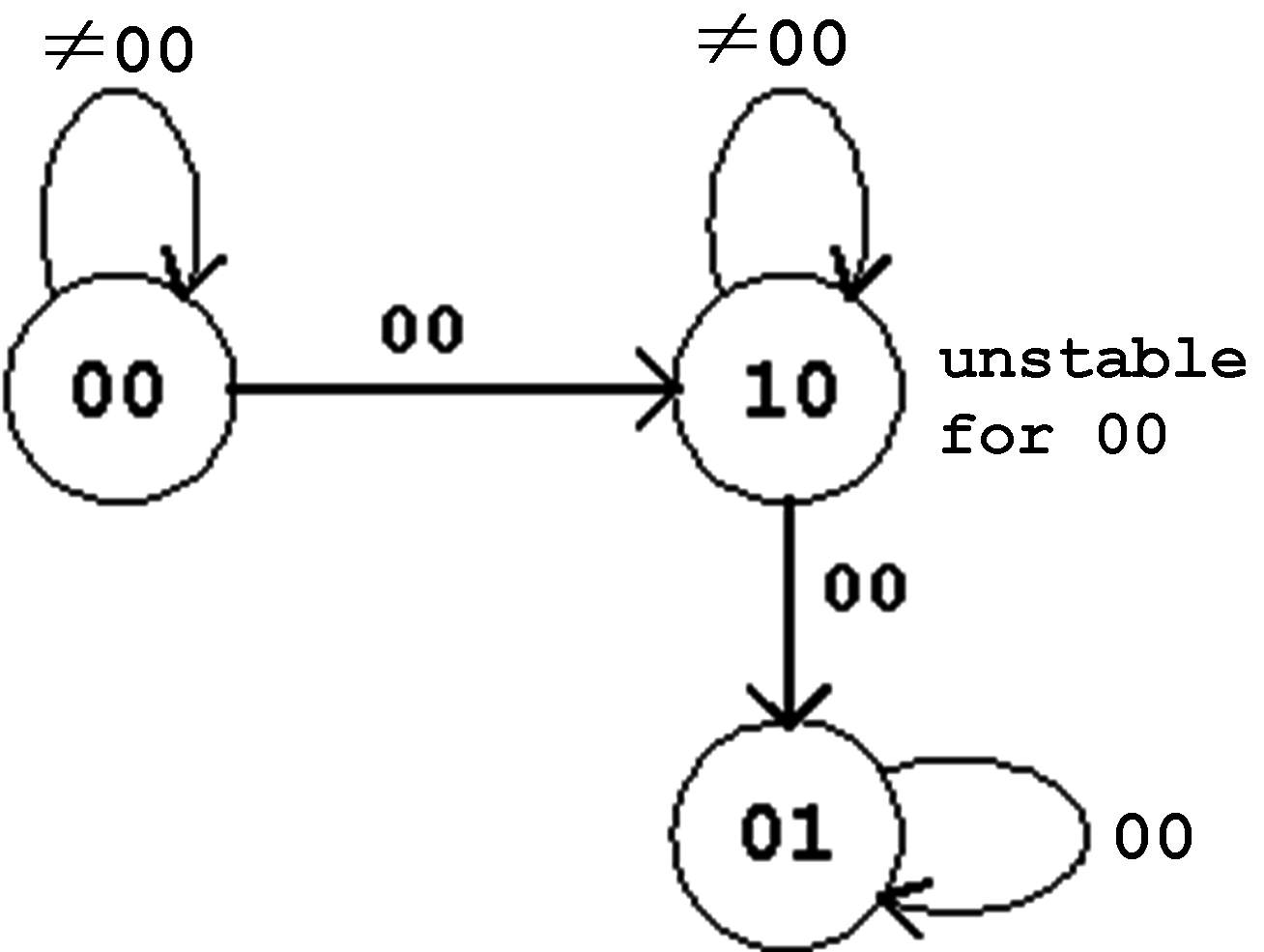

Using the function table and the state transition diagram these conditions can be clarifies:

| Figure 6.2: Asynchronous Finite State Machine. Function Table (above) and State Diagram (right). The last column in the table shows the path to the stable state (3). |

|

Function Table and State Diagram show that the stable state will only be reached after passing a sequence:

With constant inputs x1 = x2 = 0

the asynchronous FSM will first switch into the state

v1, v2 = 1,0 = z1,

z2 .

After the gate propagation delay times have passed both feedback lines will change their values:

v1: '1'  '0' and v2: '0'

'0' and v2: '0'  '1' .

'1' .

Only with these feedback values the outputs of the combinational circuit will assume stable values.

Hint:

In the synchronous Finite State Machine the prerequisite for stability is always given; the subsequent state will always be assumed with the next clock signal.

But the triggering edge may only occur after all output signals have assumed stable values.

| Figure 6.3: Synchronous Finite State Machine. Function Table (above) and State Diagram (right). |

|

In a synchronous finite state machine all states are stable.

Synchronous FSMs are more "good-natured" than asynchronous ones, because it is determined externally when the next state will be assumed. In asynchronous FSMs the signal changes at the feedback inputs depend on the gate delay times.

Synchronous finite state machines can be designed fail safe, but in general they are running more slowly than the asynchronous ones.

| Contents | Previous Chapter | Next Chapter |